We design systems with LEON and NOEL-V processors.

We develop custom extensions for LEON and NOEL-V processors.

We provide software and hardware support for LEON and NOEL-V processors.

For floating-point processing in the LEON and NOEL-V processors we offer a highly configurable floating-point unit (daiFPU) that complies with the IEEE 754 (2019) standard. In addition, daiFPU supports complex arithmetic and user-defined floating-point number formats, a feature that is beneficial for deep learning.

For fixed-point processing in LEON and NOEL-V we offer an implementation of SIMD operations within a processor register (SWAR) targeted at GNSS processing, low-precision deep learning inference and audio/video processing.

Software performance can be accelerated with new floating-point and integer data types that can be compiled with our customized version of the LLVM compiler.

Demos are available for AMD, Microchip and NanoXplore FPGAs.

News

Presenting SWAR for Image Compression at RISC-V in Space

We will attend the RISC-V in Space Workshop, organized by Frontgrade Gaisler in Göteborg, Sweden on April 2-3, 2025, where we will present a poster with our work on acceleration of lossless image compression (CCSDS121) executed in RISC-V, demonstrating improved performance and energy efficiency while using only a few hundred look-up tables and registers for a custom processor instruction that computes an optimal Rice code.

Date: 2025/03/31

AGGA-4 IP Core Talk at SEFUW

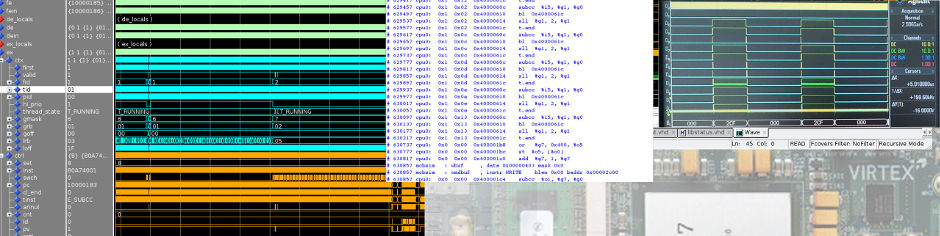

We will present the new AGGA-4 IP Core at the SEFUW workshop, organized at ESTEC, Noordwijk, the Netherlands on March 25-27, 2025. The talk will describe its features and the major design choices made during the design process, notably those that significantly improve the performance of DMA transfers of GNSS observables when compared to the AGGA-4 ASIC, the adoption of the technology mapping library from the LEON2-FT IP core, and newly implemented features that enable cycle-by-cycle debugging of GNSS software. The talk will conclude with implementation characteristics of the AGGA-4 IP core.

Date: 2025/03/18

First version of the AGGA-4 IP core delivered to ESA

We have delivered the first version of the AGGA-4 IP core to ESA. The AGGA-4 IP core uses the same address map like the AT7991 AGGA-4 ASIC. When combined with the LEON2-FT IP core, it can execute programs designed for AT7991. The AGGA-4 IP core features a technology mapping library that makes it easily portable across a wide range of implementation targets. Demos are available for the AMD and Microchip FPGAs.

Date: 2023/12/06

SpacE FPGA Users Workshop

We will present the SWAR concept, developed for instruction set extensions in LEON2 and NOEL-V, at the SEFUW workshop, organized at ESTEC, Noordwijk, the Netherlands on March 14-16, 2023. Besides describing the concept in general, we will discuss its applicability to speeding-up CCSDS121 image compression in LEON2-FT, and conclude with a presentation of enhanced LEON2-FT that uses an embedded FPGA for implementation of user-defined instructions.

Date: 2023/03/12

RISC-V in Space

We will discuss floating-point and fixed-point performance of the NOEL-V processor from Cobham Gaisler at the ESA workshop about RISC-V for space, organized at ESTEC, Noordwijk, the Netherlands on December 14, 2022. The discussion will be based on performance data measured for the CoreMark-Pro and FPMark benchmarks from EEMBC, executed on a variety of NOEL-V multi-core configurations with three different FPUs. We will also demonstrate NOEL-V with our arithmetic extensions implemented in NanoXplore NG-Large and Xilinx Kintex UltraScale.

Date: 2022/12/08

The daiteq arithmetic extensions also available for GRLIB 2022.2

We are pleased to announce that our floating-point and fixed-point arithmetic extensions are available also for the LEON3 and NOEL-V processors provided in GRLIB 2022.2. The extensions are built on top of the highly configurable daiteq floating-point unit and the SWAR unit, developed within an ESA-funded activity, and supported by an llvm compiler with daiteq extensions. More information about the arithmetic extensions is provided on the Products page. Information about the extended llvm compiler and example programs is provided on the Software page.

Date: 2022/11/21

Awarded ESA contract to retarget AGGA-4 to space-qualified FPGAs

We have been awarded a contract with the European Space Agency to retarget the existing AGGA-4 ASIC implementation to current space-qualified FPGAs. As a result of this activity future ESA missions will be able to use more cost- and resource-efficient implementations of the AGGA-4 IP core.

Date: 2022/09/14

NOEL-V floating-point performance in GRLIB 2022.1

The newest GRLIB update, released by Cobham Gaisler in March, implements a more efficient floating-point interface in NOEL-V that results in better floating-point performance. The following table compares measurements for NOEL-V in GRLIB 2022.1 with the previous GRLIB 2021.2, as well as LEON2. (single-core execution in RTEMS, gcc)

Benchmark |

Units |

NOEL-V RV64 (2022.1) |

NOEL-V RV64 (2021.2) |

LEON2 |

||

|---|---|---|---|---|---|---|

. |

. |

nanoFPUnv |

daiFPUrv |

nanoFPUnv |

daiFPUrv |

daiFPU |

Whetstone |

||||||

binary64 |

kWIPS/MHz |

167 |

417 |

158 |

326 |

399 |

binary32 |

kWIPS/MHz |

210 |

443 |

194 |

341 |

481 |

Linpack rolled |

||||||

binary64 |

kflops/MHz |

30 |

60 |

26 |

41 |

55 |

binary32 |

kflops/MHz |

32 |

64 |

27 |

45 |

68 |

Linpack unrolled |

||||||

binary64 |

kflops/MHz |

30 |

59 |

26 |

43 |

58 |

binary32 |

kflops/MHz |

32 |

63 |

28 |

47 |

74 |

The measured values show some interesting features. Contrary to the previous version, in GRLIB 2022.1 the unrolled Linpack shows slightly worse performance than the rolled version. In addition, NOEL-V with daiFPU achieves almost the same floating-point performance as LEON2 with daiFPU for binary64. Regarding binary32, we attribute the slightly lower floating-point performance in NOEL-V to the fact that in a 64-bit NOEL-V implementation fetching and processing 32-bit values is probably less efficient that in a 32-bit LEON2.

Date: 2022/04/13

Demo programs for LEON with daiteq extensions

The LEON arithmetic extensions designed by daiteq implement reduced-precision floating-point and fixed-point arithmetic in LEON2. The Software page provides instructions for downloading demo programs that show how the extensions can be used in C programs and compiled for LEON2.

Date: 2021/10/29

FMC-SRAM board for the NG-Medium and NG-Large development kits

We have designed an FMC-SRAM board that can be used also with the NanoXplore NG-Medium and NG-Large development kits. For a full description and ordering information check the FMC-SRAM board page.

Date: 2021/10/14

NOEL-V single-core floating-point performance

How does NOEL-V perform for classical workloads? (grlib 2021.2, single-core execution in RTEMS, gcc)

Benchmark |

Units |

NOEL-V (HPP64) |

LEON2 |

|

|---|---|---|---|---|

. |

. |

nanoFPUnv |

daiFPUrv |

daiFPU |

Whetstone |

||||

binary64 |

kWIPS/MHz |

158 |

326 |

399 |

binary32 |

kWIPS/MHz |

194 |

341 |

481 |

Linpack rolled |

||||

binary64 |

kflops/MHz |

26 |

41 |

55 |

binary32 |

kflops/MHz |

27 |

45 |

68 |

Linpack unrolled |

||||

binary64 |

kflops/MHz |

26 |

43 |

58 |

binary32 |

kflops/MHz |

28 |

47 |

74 |

Date: 2021/09/16

Evaluation of NOEL-V

We are evaluating the performance and scalability of the NOEL-V RISC-V processor, kindly provided by Cobham Gaisler, for use in future ESA missions. In the next step we will extend NOEL-V with our arithmetic extensions that we have developed for LEON2FT. More information is available in the press release.

Date: 2020/12/11

daiFPU vs. Meiko

How does daiFPU compare with the Meiko FPU? (llvm10)

Benchmark |

Units |

daiFPU (LEON2) |

Meiko (AT697F) |

|---|---|---|---|

Whetstone |

|||

binary64 |

kWIPS/MHz |

289 |

283 |

binary32 |

kWIPS/MHz |

324 |

323 |

Linpack rolled |

|||

binary64 |

kflops/MHz |

55 |

49 |

binary32 |

kflops/MHz |

72 |

83 |

Linpack unrolled |

|||

binary64 |

kflops/MHz |

59 |

50 |

binary32 |

kflops/MHz |

79 |

84 |

Date: 2020/10/09

Enhanced LEON2FT with daiFPU and SWAR delivered to ESA

We have delivered the new LEON2FT with our daiFPU and SWAR extensions to ESA. The extended LEON2FT will be used in future ESA missions. The delivery included synthesizable VHDL sources, testing environment, coverage data and software toolchain. Besides daiFPU and SWAR the LEON2FT also features new system profiling registers.

Date: 2020/09/29